# 400G QSFP-DD FR4 Transceiver

ET7502-FR4

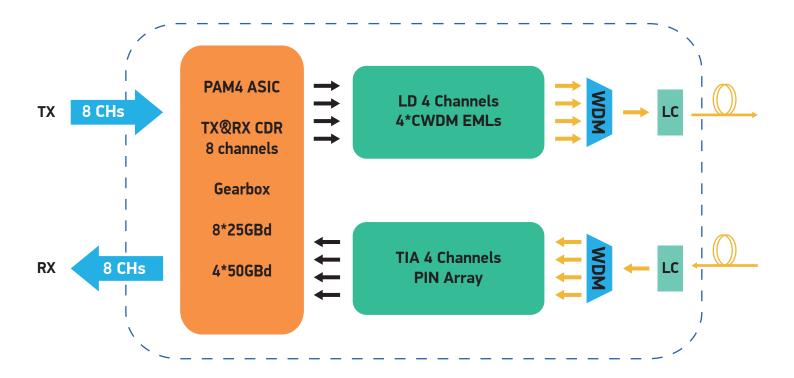

Edgecore's QSFP-DD 400Gbps transceiver module is designed for optical communication applications over 400 Gigabit Ethernet links of up to 2 km single mode fiber. This product has 8 independent electrical input/output channels that convert 50Gbps (PAM4) electrical input data to 4 channels of 100Gbps (PAM4) optical signals. The electrical interface of the module is compliant with the 400GAUI-8 interface as defined by IEEE 802.3bs, and compliant with QSFP-DD MSA.

#### **Product Features**

- Single 3.3 V power supply

- Power dissipation < 10 W

- Up to 2 km over SMF fiber

- QSFP-DD MSA compliant

- 8x53.125 Gbps (PAM4) electrical interface

- Duplex LC connector

- Commercial case temperature range of 0°C to 70°C

- PIN and TIA array on the receiver side

- I2C interface with integrated Digital Diagnostic Monitoring

- RoHS compliant

## **Applications**

- 400G-FR4 applications

- Data center

- Enterprise networking

- Infiniband interconnects

### **Ordering Information**

| Part Number | Data Rate | Fiber | Distance | Interface | Temp.   | DDMI | CMIS             |

|-------------|-----------|-------|----------|-----------|---------|------|------------------|

| ET7502-FR4  | 425 Gbps  | SMF   | 2 km     | LC        | 0~+70°C | Yes  | CMIS4.0 *(note1) |

Note 1: CMIS4.0 or later versions

# **Transmitter Optical Characteristics**

| Parameter                                                                                                                 | Symbol                      | Minimum      | Typical | Maximum | Unit  |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------|---------|---------|-------|

| Signaling Speed per Lane                                                                                                  |                             |              | 53.125  |         | GBd   |

| Modulation Format                                                                                                         |                             |              | PAM4    |         |       |

| Lane_0 Center Wavelength                                                                                                  | λC0                         | 1264.5       |         | 1277.5  | nm    |

| Lane_1 Center Wavelength                                                                                                  | λC1                         | 1284.5       |         | 1297.5  | nm    |

| Lane_2 Center Wavelength                                                                                                  | λC2                         | 1304.5       |         | 1317.5  | nm    |

| Lane_3 Center Wavelength                                                                                                  | усз                         | 1324.5       |         | 1337.5  | nm    |

| Side-mode Suppression Ratio                                                                                               | SMSR                        | 30           |         |         | dB    |

| Total Average Launch Power                                                                                                |                             |              |         | 9.3     | dBm   |

| Average Launch Power, Each Lane *(note 1)                                                                                 | TxAVG                       | -3.3         |         | 3.5     | dBm   |

| Outer Optical Modulation Amplitude (OMA <sub>outer</sub> ),<br>Each Lane* <sup>(note 2)</sup>                             | TxOMA                       | -0.3         |         | 3.7     | dBm   |

| Difference in Launch Power Between Any Two<br>Lanes (OMA <sub>outer</sub> )                                               |                             |              |         | 4       | dB    |

| Launch Power in OMA $_{outer}$ Minus TDECQ, Each Lane: For Extinction Ratio $\geq 4.5~dB$ For Extinction Ratio $< 4.5~dB$ | OMA <sub>outer</sub> -TDECQ | -1.7<br>-1.6 |         |         | dBm   |

| Transmitter and Dispersion Eye Closure for PAM4 (TDECQ), Each Lane                                                        | TDECQ                       |              |         | 3.4     | dB    |

| TDECQ-10*log10 (Ceq), Each Lane*(note 3)                                                                                  |                             |              |         | 3.4     | dB    |

| Average Launch Power of OFF Transmitter, Each Lane                                                                        |                             |              |         | -20     | dBm   |

| Extinction Ratio                                                                                                          | ER                          | 3.5          |         |         | dB    |

| Transmitter Transition Time                                                                                               |                             |              |         | 17      | ps    |

| RIN17.1 OMA                                                                                                               |                             |              |         | -136    | dB/Hz |

| Optical Return Loss Tolerance                                                                                             |                             |              |         | 17.1    | dB    |

| Transmitter Reflectance*(note 4)                                                                                          |                             |              |         | -26     | dB    |

<sup>\*</sup>Note 1: Average launch power, each lane (min) is informative and not the principal indicator of signal strength. A transmitter with launch power below this value cannot be compliant; however, a value above this does not ensure compliance.

<sup>\*</sup>Note 2: Even if the TDECQ < 1.4 dB for an extinction ratio of ≥ 4.5 dB or TDECQ < 1.3 dB for an extinction ratio of < 4.5 dB, the OMAouter (min) must exceed this value.

<sup>\*</sup>Note 3: Ceq is a coefficient defined in IEEE Std 802.3-2018 clause 121.8.5.3 which accounts for reference equalizer noise enhancement.

<sup>\*</sup>Note 4: Transmitter reflectance is defined looking into the transmitter.

## **Receiver Optical Characteristics**

| Parameter                                                                          | Symbol | Minimum | Typical | Maximum                 | Unit |

|------------------------------------------------------------------------------------|--------|---------|---------|-------------------------|------|

| Signaling Speed per Lane                                                           |        |         | 53.125  |                         | GBd  |

| Lane_0 Center Wavelength                                                           | λСО    | 1264.5  |         | 1277.5                  | nm   |

| Lane_1 Center Wavelength                                                           | λC1    | 1284.5  |         | 1297.5                  | nm   |

| Lane_2 Center Wavelength                                                           | λC2    | 1304.5  |         | 1317.5                  | nm   |

| Lane_3 Center Wavelength                                                           | уСЗ    | 1324.5  |         | 1337.5                  | nm   |

| Damage Threshold Each Lane*(note 1)                                                |        | 4.5     |         |                         | dBm  |

| Average Receive Power Each Lane*(note 2)                                           | RxAVG  | -7.3    |         | 3.5                     | dBm  |

| Receive Power (OMA <sub>outer</sub> ) Each Lane                                    | RxOMA  |         |         | 3.7                     | dBm  |

| Difference in Receive Power Between Any Two Lanes (OMA <sub>outer</sub> )          |        |         |         | 4.1                     | dB   |

| Receiver Reflectance                                                               |        |         |         | -26                     | dB   |

| Receiver Sensitivity (OMA $_{\rm outer}$ ), Each Lane $^{\star ({\rm note} \; 3)}$ | SenOMA |         |         | max<br>(-4.6, SECQ-6.0) | dBm  |

| Stressed Receiver Sensitivity (OMA <sub>outer</sub> ), Each Lane*(note 4)          |        |         |         | -2.6                    | dBm  |

| Conditions of Stressed Receiver Sensitivity Test:                                  |        |         |         |                         |      |

| Stressed Rye Closure for PAM4 (SECQ), Lane<br>Under Test                           | SECQ   |         | 3.4     |                         | dB   |

| SECQ-10*log10 (Ceq), Lane Under Test*(note 5)                                      |        |         |         | 3.4                     | dB   |

| OMA <sub>outer</sub> of Each Aggressor Lane                                        |        |         | 1.5     |                         | dBm  |

| LOS Assert                                                                         | LOSA   | -15     |         |                         | dBm  |

| LOS De-Assert                                                                      | LOSD   |         |         | -9.5                    | dBm  |

| LOS Hysteresis                                                                     |        | 0.5     |         |                         | dB   |

<sup>\*</sup>Note 1: The receiver shall be able to tolerate, without damage, continuous exposure to an optical signal having this average power level. The receiver does not have to operate correctly at this input power.

<sup>\*</sup>Note 2: Average receive power, each lane (min) is informative and not the principal indicator of signal strength. A received power below this value cannot be compliant; however, a value above this does not ensure compliance.

<sup>\*</sup>Note 3: Measured with conformance test signal at TP3 for the BER specified in IEEE Std 802.3-2018 clause

<sup>\*</sup>Note 4: Receiver sensitivity (OMA<sub>outer</sub>), each lane (max) is informative and is defined for a transmitter with a value of SECQ up to 3.4 dB.

<sup>\*</sup>Note 5: Ceq is a coefficient defined in IEEE Std 802.3-2018 clause 121.8.5.3 which accounts for reference equalizer noise enhancement.

## **Absolute Maximum Ratings**

| Parameter                                                             | Symbol | Min. | Max. | Unit |  |  |

|-----------------------------------------------------------------------|--------|------|------|------|--|--|

| Storage Temperature                                                   | Ts     | -40  | +85  | °C   |  |  |

| Supply Voltage                                                        | Vcc    | -0.5 | 3.6  | V    |  |  |

| Damage Threshold                                                      | Rxdmg  | 4.5  |      | dBm  |  |  |

| *Exceeding any one of these values may damage the device permanently. |        |      |      |      |  |  |

### **Recommended Operating Conditions**

| Parameter                   | Symbol | Min.  | Typical | Max.  | Unit |

|-----------------------------|--------|-------|---------|-------|------|

| Operating Case Temperature  | Tc     | 0     |         | 70    | °C   |

| Power Supply Voltage        | Vcc    | 3.135 | 3.3     | 3.465 | V    |

| Operating Relative Humidity | RH     | 0     |         | 85    | %    |

| Power Dissipation           | PD     |       |         | 10    | W    |

<sup>\*</sup> Power Supply specifications, Instantaneous, sustained and steady state current compliant with QSFP-DD MSA Power Classification.

#### **Transmitter Electrical Characteristics**

| Parameter                                                      | Symbol | Min.  | Тур. | Max  | Unit       | Notes                          |

|----------------------------------------------------------------|--------|-------|------|------|------------|--------------------------------|

| Differential Data Input Swing per<br>Lane* <sup>(note 1)</sup> |        | 900   |      |      | $mV_{p-p}$ |                                |

| Differential Input Impedance                                   | Zin    | 90    | 100  | 110  | ohm        |                                |

| Stressed Input Parameters                                      |        |       |      |      |            |                                |

| Eye Width                                                      |        | 0.265 |      |      | UI         | @TP4, all 3<br>PAM4 eyes, 1E-5 |

| DC Common Mode Voltage*(note 2)                                |        | -350  |      | 2850 | mV         |                                |

## **Receiver Electrical Characteristics**

| Parameter                     | Symbol                         | Min.  | Тур. | Max | Unit       | Notes                          |

|-------------------------------|--------------------------------|-------|------|-----|------------|--------------------------------|

| Differential Output Amplitude |                                |       |      | 900 | $mV_{p-p}$ |                                |

| Differential Output Impedance | Zout                           | 90    | 100  | 110 | ohm        |                                |

| Output Rise/Fall Time         | t <sub>r</sub> /t <sub>f</sub> | 9.5   |      |     | ps         | 20%~80%                        |

| Eye Width                     |                                | 0.265 |      |     | UI         |                                |

| Eye Height Differential       |                                | 70    |      |     | mV         | @TP4, all 3<br>PAM4 eyes, 1E-5 |

<sup>\*</sup>Notes 1: With the exception to IEEE 802.3bs 120E.3.1.2 that the pattern is PRBS31Q or scrambled idle.

<sup>\*</sup>Notes 2: DC common mode voltage is generated by the host. Specification includes effects of ground offset voltage.

# **Transceiver Block Diagram**

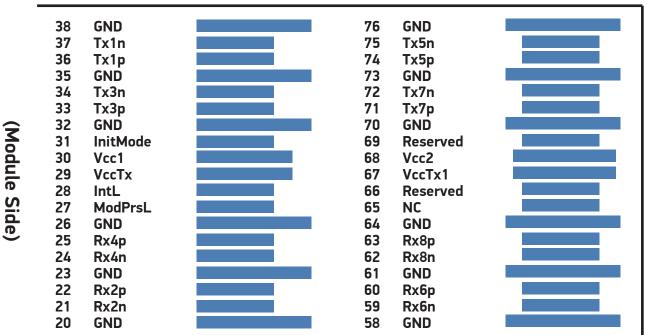

## **QSFP-DD Transceiver Electrical Pad Layout**

Module Card Edge (Host Side)

Top side viewed from top Legacy QSFP28 **Additional Pads QSFP-DD Pads GND** 39 **GND** 1 2 Tx6n 40 Tx2n Module Card Edge (Host Side) Tx6p 41 Tx2p 3 **GND** 42 **GND** 4 Tx8n 43 Tx4n 5 Tx8p 44 Tx4p 6 **GND** 45 GND Reserved 46 ModselL 8 9 VS<sub>1</sub> 47 ResetL VccRx1 48 **VccRx** 10 SCL 11 VS2 49 VS3 50 **SDA** 12 51 **GND GND** 13 52 Rx7p Rx3p 14 Rx7n 53 Rx3n 15 **GND** 54 **GND** 16

17

18

19

Rx1p

Rx1n

**GND**

Bottom side viewed from bottom **Additional** Legacy QSFP28 **OSFP-DD Pads Pads**

55

56

57

Rx5p

Rx5n

**GND**

# **Pin Descriptions**

| Pin | Logic       | Symbol  | Description                         | Notes |

|-----|-------------|---------|-------------------------------------|-------|

| 1   |             | GND     | Ground                              | 1     |

| 2   | CML-I       | Tx2n    | Transmitter Inverted Data Input     |       |

| 3   | CML-I       | Tx2p    | Transmitter Non-Inverted Data Input |       |

| 4   |             | GND     | Ground                              | 1     |

| 5   | CML-I       | Tx4n    | Transmitter Inverted Data Input     |       |

| 6   | CML-I       | Тх4р    | Transmitter Non-Inverted Data Input |       |

| 7   |             | GND     | Ground                              | 1     |

| 3   | LVTTL-I     | ModSelL | Module Select                       |       |

| 9   | LVTTL-I     | ResetL  | Module Reset                        |       |

| 10  |             | VccRx   | +3.3 V Power Supply Receiver        | 2     |

| 11  | LVCMOS- I/O | SCL     | 2-wire serial interface clock       |       |

| 12  | LVCMOS- I/O | SDA     | 2-wire serial interface data        |       |

| 13  |             | GND     | Ground                              | 1     |

| 14  | CML-0       | Rx3p    | Receiver Non-Inverted Data Output   |       |

| 15  | CML-0       | Rx3n    | Receiver Inverted Data Output       |       |

| 16  |             | GND     | Ground                              | 1     |

| 17  | CML-0       | Rx1p    | Receiver Non-Inverted Data Output   |       |

| 18  | CML-0       | Rx1n    | Receiver Inverted Data Output       |       |

| 19  |             | GND     | Ground                              | 1     |

| 20  |             | GND     | Ground                              | 1     |

| 21  | CML-0       | Rx2n    | Receiver Inverted Data Output       |       |

| 22  | CML-0       | Rx2p    | Receiver Non-Inverted Data Output   |       |

| 23  |             | GND     | Ground                              | 1     |

| 24  | CML-0       | Rx4n    | Receiver Inverted Data Output       |       |

| 25  | CML-0       | Rx4p    | Receiver Non-Inverted Data Output   |       |

| 26  |             | GND     | Ground                              | 1     |

| 27  | LVTTL-0     | ModPrsL | Module Present                      |       |

| 28  | LVTTL-0     | IntL    | Interrupt                           |       |

| 29  |             | VccTx   | +3.3 V Power supply transmitter     | 2     |

| 30  |             | Vcc1    | +3.3 V Power supply                 | 2     |

| 31  | LVTTL-I     | LPMode  | Low Power Mode                      |       |

| 32  |             | GND     | Ground                              | 1     |

| 33  | CML-I       | Тх3р    | Transmitter Non-Inverted Data Input |       |

| 34  | CML-I       | Tx3n    | Transmitter Inverted Data Input     |       |

| 35  |             | GND     | Ground                              | 1     |

| 36  | CML-I       | Tx1p    | Transmitter Non-Inverted Data Input |       |

| 37  | CML-I       | Tx1n    | Transmitter Inverted Data Input     |       |

| 38  |             | GND     | Ground                              | 1     |

| 39  |             | GND     | Ground                              | 1     |

| 40  | CML-I       | Tx6n    | Transmitter Inverted Data Input     |       |

| 41  | CML-I       | Тх6р    | Transmitter Non-Inverted Data Input |       |

| 42  |             | GND     | Ground                              | 1     |

## **Pin Descriptions**

| Pin | Logic | Symbol   | Description                         | Notes |

|-----|-------|----------|-------------------------------------|-------|

| 43  | CML-I | Tx8n     | Transmitter Inverted Data Input     |       |

| 44  | CML-I | Tx8p     | Transmitter Non-Inverted Data Input |       |

| 45  |       | GND      | Ground                              | 1     |

| 46  |       | Reserved | For future use                      | 3     |

| 47  |       | VS1      | Module Vendor Specific 1            | 3     |

| 48  |       | VccRx1   | 3.3 V Power Supply                  | 2     |

| 49  |       | VS2      | Module Vendor Specific 2            | 3     |

| 50  |       | VS3      | Module Vendor Specific 3            | 3     |

| 51  |       | GND      | Ground                              | 1     |

| 52  | CML-0 | Rx7p     | Receiver Non-Inverted Data Output   |       |

| 53  | CML-0 | Rx7n     | Receiver Inverted Data Output       |       |

| 54  |       | GND      | Ground                              | 1     |

| 55  | CML-0 | Rx5p     | Receiver Non-Inverted Data Output   |       |

| 56  | CML-0 | Rx5n     | Receiver Inverted Data Output       |       |

| 57  |       | GND      | Ground                              | 1     |

| 58  |       | GND      | Ground                              | 1     |

| 59  | CML-0 | Rx6n     | Receiver Inverted Data Output       |       |

| 50  | CML-0 | Rx6p     | Receiver Non-Inverted Data Output   |       |

| 51  |       | GND      | Ground                              | 1     |

| 52  | CML-0 | Rx8n     | Receiver Inverted Data Output       |       |

| 53  | CML-0 | Rx8p     | Receiver Non-Inverted Data Output   |       |

| 64  |       | GND      | Ground                              | 1     |

| 55  |       | NC       | No Connect                          | 3     |

| 66  |       | Reserved | For future use                      | 3     |

| 67  |       | VccTx1   | 3.3 V Power Supply                  | 2     |

| 58  |       | Vcc2     | 3.3 V Power Supply                  | 2     |

| 59  |       | Reserved | For Future Use                      | 3     |

| 70  |       | GND      | Ground                              | 1     |

| 71  | CML-I | Тх7р     | Transmitter Non-Inverted Data Input |       |

| 72  | CML-I | Tx7n     | Transmitter Inverted Data Input     |       |

| 73  |       | GND      | Ground                              | 1     |

| 74  | CML-I | Тх5р     | Transmitter Non-Inverted Data Input |       |

| 75  | CML-I | Tx5n     | Transmitter Inverted Data Input     |       |

| 76  |       | GND      | Ground                              | 1     |

<sup>\*</sup>Note 1: QSFP-DD uses common ground (GND) for all signals and supply (power). All are common within the QSFP-DD module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

<sup>\*</sup>Note 2: VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination.

The connector Vcc pins are each rated for a maximum current of 1000 mA.

<sup>\*</sup>Note 3: All Vendor Specific, Reserved and No Connect pins may be terminated with 50 ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF.

## **Datasheet**

## **Transceiver**

#### Warranty

Please check www.edge-core.com for the warranty terms in your country.

#### For More Information

To find out more about Edgecore Networks Corporation products and solutions, visit www.edge-core.com.

#### **About Edgecore Networks Corporation**

Edgecore Networks Corporation is in the business of providing innovative network solutions. In the service provider network, in the data center or in the cloud, Edgecore Networks Corporation delivers the software and systems that transform the way the world connects. Edgecore Networks Corporation serves customers and partners worldwide. Additional information can be found at www.edge-core.com.

Edgecore Networks Corporation is a subsidiary of Accton Technology Corporation, the leading network ODM company. The Edgecore data center switches are developed and manufactured by Accton.

To purchase Edgecore Networks solutions, please contact your Edgecore Networks Corporation representatives at +886 3 563 8888 (HQ) or +1 (949)-336-6801 or authorized resellers.

© Copyright 2022 Edgecore Networks Corporation. The information contained herein is subject to change without notice. This document is for informational purposes only and does not set forth any warranty, expressed or implied, concerning any equipment, equipment feature, or service offered by Edgecore Networks Corporation. Edgecore Networks Corporation shall not be liable for technical or editorial errors or omissions contained herein.

www.edge-core.com